Hyperlink

About HyperLink

HyperLink is a high speed chip-to-chip interface developed by Texas Instruments that connects:

• TI KeyStone devices to each other

OR

• TI Keystone device to an FPGA

HyperLink provides a high-speed, low-latency, and low-pin-count communication interface that extends the internal CBA 3.x-based transactions between two KeyStone devices or between a KeyStone device and FPGA by utilizing the Integretek HyperLink FPGA core. It can emulate all currently-used peripheral interface mechanisms. HyperLink includes the data signals and the sideband control signals. The data signals are SerDes-based and the sideband control signals are LVCMOS-based. The current version of HyperLink offers point-to-point connection between two devices.

Integretek HyperLink FPGA IP

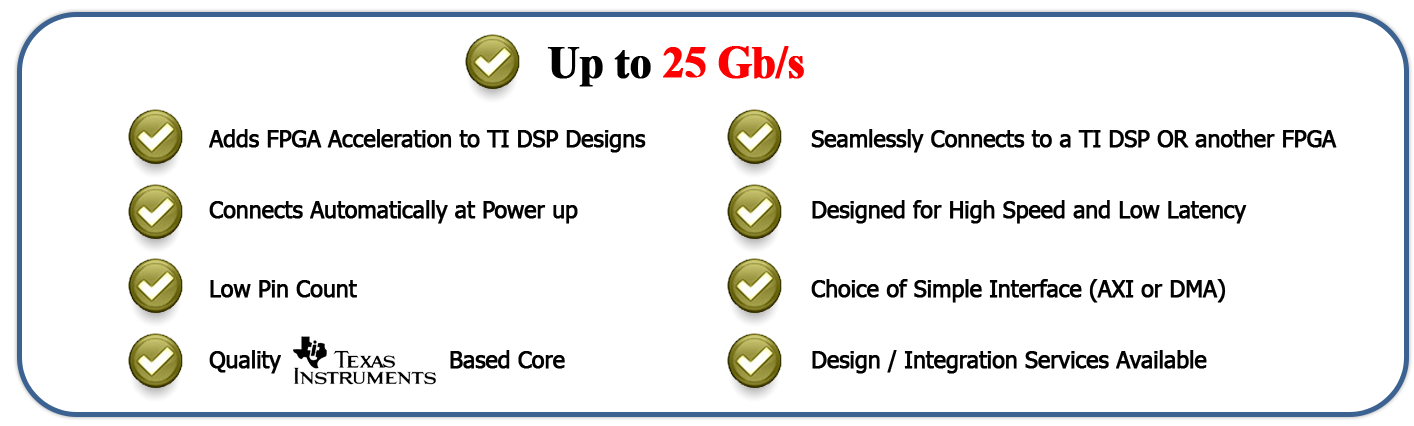

The Integretek HyperLink Core allows the creation of a user defined system which can communicate with remote TI Cx66 DSP devices via a high speed SERDES interface. The core provides a high-speed communication interface that extends the AXI interface over a serial connection. The HyperLink FPGA core leverages the same proven HyperLink IP used within the TI multi-core DSPs. The core is available with either an industry standard AXI interface or an easy to use DMA interface.

The HyperLink FPGA core supports the following features:

- Up to 25Gbps transfer rate (4 lane)

- Point-to-point connection

- Link self-initializes

- Supports multiple outstanding read, write and interrupt transactions

- Simple packet-based transfer protocol for memory mapped access

- AXI4 Interface Complies with AMBA AXI Protocol V2.0

- 64 user defined interrupt inputs, level and pulse sensitive

- AXI4 Slave (transmit to DSP and Control Register access)

- AXI4 Master (receive from DSP)

- Optional DMA interface

Supported Devices

HyperLink is available on a wide range of Altera and Xilinx device families from high performance, high density devices to cost sensitive, low power devices.

Click on the graphics below for more details on the HyperLink core for your specific device.

Developing HyperLink Solutions

Integretek offers solutions to accelerate your HyperLink development. This section provides details on development solutions for your device.

Integretek has engineered development boards that provide an efficient and verified path to develop and test your unique HyperLink solution. The HyperLink Connectivity Cards are designed to provide connectivity between HyperLink enabled Texas Instruments DSP EVM boards and FPGA based development platforms.

Integretek HyperLink Evaluation Modules take that one step further bringing the FPGA and DSP together on a single board allowing for at speed testing. Select the product of interest below for more detailed information.

Documents

HyperLink High Speed DSP Interface FPGA Core Data Sheet

Texas Instruments KeyStone Architecture HyperLink User Guide

This document provides a detailed description of the Texas Instruments HyperLink interface.

Texas Instruments C66x KeyStone Training – HyperLink

This document provides a high level overview of the HyperLink interface.

Texas Instruments Hardware Design Guide for KeyStone Devices

This document describes hardware system design considerations for the KeyStone family of processors including implementing a HyperLink interface.

Frequently Asked Questions

What data rates are supported by the HyperLink FPGA IP?

The HyperLink core supports a single channel rate of 1.25 Gbps, 3.125 Gbps and 6.25 Gbps for a four channel aggregate rate of 5, 12.5 and 25 Gbps respectively. Check the FPGA Cores page for details on what core speeds your specific device will support as supported rates may vary depending on the FPGA SERDES.

Can the core change speeds, how is this done?

Certain versions of the Hyperlink core can change speeds. Top level signals are provided to strap the core to a particular speed. It is recommended that the core be put through a full reset sequence each time the speed is changed.

What input clock is required for HyperLink?

The HyperLink core requires a 156.25 MHz SERDES input clock

Will the HyperLink data rate adjust if I use a different input clock speed?

No – the core requires the 156.25 MHz clock to meet spec.

What HyperLink Connectivity Card do I use with my FPGA dev board?

Information on what Connectivity Card to use can be found here.

How is the core licensed?

The core is sold as a x1 or x4 configuration, with a royalty free perpetual license allowing the core to be used in multiple designs and multiple instantiations. Licenses can be a fixed node or floating seat.

What is delivered with the core?

In addition to the encrypted core you will receive a Testbench and Verification Environment, an Example HyperLink project and HyperLink User Guide Documentation.

What is included with the Verification Environment?

A Verilog environment is provided that includes; testbench, sample tests, and scripts.

How long does the simulation environment have to run before hyperlink activity can be observed?

Some versions of the Hyperlink simulation environment require up to 1.1ms of simulation time before link activity can be observed. This is due to the time it takes the PLL models to lock when in dynamic reconfiguration mode.