# KeyStone Architecture HyperLink

**User Guide**

Literature Number: SPRUGW8C June 2013

# **Release History**

| Release  | Date          | Description/Comments                                                                                                                             |

|----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| SPRUGW8C | June 2013     | • Corrected pin number from 24 pins to 26 pins (Page 1-2)                                                                                        |

|          |               | Made corrections to the Address Translation at RX Side graphic. (Page 2-22)                                                                      |

|          |               | Fixed minor typos (Page 2-22)                                                                                                                    |

|          |               | Corrected the segment size (Page 2-23)                                                                                                           |

|          |               | Corrected typo in the formula (Page 2-23)                                                                                                        |

|          |               | • Fixed typo in the register chapter 3.2.9 (Page 3-11)                                                                                           |

| SPRUGW8B | October 2012  | Added Side band state register for Keystone II Hyperlink (Page 3-17)                                                                             |

|          |               | Added Rx Priority Control register for Keystone II devices (Page 3-17)                                                                           |

|          |               | Added Rx Priority Control register for Keystone II devices (Page 3-15)                                                                           |

|          |               | Added RTL version and revmin for Keystone II devices (Page 3-4)                                                                                  |

|          |               | Added section HyperLink SerDes Training Process (Page 2-11)                                                                                      |

|          |               | • Updated SERDES programming chapter to enable PLL after running all Tx, Rx configuration (Page A-2)                                             |

|          |               | Add Link Status Register in the index table (Page 3-2)                                                                                           |

|          |               | Added link status register in the register map table (Page 3-2)                                                                                  |

|          |               | Modified several register descriptions for clarification (Page 3-4)                                                                              |

| SPRUGW8A | November 2011 | Added the appendix "Programming Examples" (Page A-1)                                                                                             |

|          |               | • Updated SerDes Configuration and Clocking to add details about the SerDes operating rate, receive interface, and transmit interface (Page 2-8) |

|          |               | • Updated registers chapter to add the HyperLink SerDes configuration and status registers. (Page 3-1)                                           |

|          |               | Updated sections in the register chapter to distinguish between Local registers, Remote registers, and SerDes registers. (Page 3-1)              |

|          |               | Changed BUSWIDTH field description (Page 3-26)                                                                                                   |

| SPRUGW8  | November 2010 | Initial Release                                                                                                                                  |

### TEXAS INSTRUMENTS

www.ti.com

# Contents

| Release History |   | ø-ii |

|-----------------|---|------|

| List of Tables  |   | ø-v  |

| List of Figures | 6 | ø-vi |

| ø-vii  |

|--------|

| ø-vii  |

| ø-vii  |

| ø-viii |

| ø-viii |

|        |

## Chapter 1

| Introduction                                  | 1-1 |

|-----------------------------------------------|-----|

| 1.1 Purpose of HyperLink                      | 1-2 |

| 1.2 Terminology Used in This Document         | 1-2 |

| 1.3 Features                                  | 1-2 |

| 1.4 Functional Block Diagram                  | 1-4 |

| 1.5 Supported Use Case Statement              |     |

| 1.6 Industry Standard(s) Compliance Statement | 1-6 |

# Chapter 2

| Architecture                                                                     | 2-1  |

|----------------------------------------------------------------------------------|------|

| 2.1 Clock Control                                                                | 2-2  |

| 2.2 Memory Map                                                                   |      |

| 2.3 Signal Descriptions                                                          |      |

| 2.4 Pin Multiplexing                                                             |      |

| 2.5 Station Management Interface                                                 |      |

| 2.5.1 Lane Activation                                                            |      |

| 2.5.2 Flow Control.                                                              |      |

| 2.5.3 Power Management                                                           |      |

| 2.6 SerDes Configuration and Clocking                                            |      |

| 2.6.1 HyperLink SerDes Operating Rate Configuration                              |      |

| 2.6.2 HyperLink SerDes Receive Interface                                         |      |

| 2.6.3 HyperLink SerDes Transmit Interface                                        |      |

| 2.6.4 HyperLink SerDes Training Process                                          |      |

| 2.7 HyperLink Protocol                                                           | 2-12 |

| 2.7.1 HyperLink Write Operations                                                 |      |

| 2.7.2 HyperLink Read Operations                                                  |      |

| 2.7.3 HyperLink Format                                                           |      |

| 2.7.3.1 General Bus Control Word                                                 | 2-17 |

| 2.7.4 Address Translation                                                        |      |

| 2.7.4.1 Address Translation on the TX Side                                       |      |

| 2.7.4.2 Address Translation on the RX Side                                       |      |

| 2.7.4.3 CBA Burst Split Operations                                               |      |

| 2.7.5 Interrupt                                                                  |      |

| 2.7.5.1 Interrupt Detection                                                      |      |

| 2.7.5.2 Interrupt Processing                                                     |      |

| 2.7.5.3 Interrupt Mapping                                                        |      |

| 2.7.6 Interrupt Generating                                                       |      |

| 2.7.6.1 Setting Interrupt Pending Register by Module Status                      |      |

| 2.7.6.2 Setting Interrupt Pending Register by Writing Interrupt Pending Register | 2-28 |

| 2.7.6.3 Setting Interrupt Pending Register by HW_event       | 2-28 |

|--------------------------------------------------------------|------|

| 2.7.6.4 Setting Interrupt Pending Register by Remote Device. |      |

| 2.7.6.5 Clearing the Interrupt Pending Register              |      |

| 2.8 Passing an Interrupt to a Remote Device                  | 2-30 |

| 2.9 Reset Considerations                                     | 2-31 |

| 2.10 Initialization                                          | 2-31 |

| 2.11 DMA Event Support                                       | 2-31 |

| 2.12 Power Management                                        |      |

| 2.13 Emulation Considerations                                |      |

# Chapter 3

| Registers                                                                        | 3-1 |

|----------------------------------------------------------------------------------|-----|

| 3.1 Register Map                                                                 |     |

| 3.2 Local HyperLink Configuration Registers                                      |     |

| 3.2.1 Revision Register (Base Address + 0x00)                                    |     |

| 3.2.2 Control Register (Base Address + 0x04)                                     |     |

| 3.2.3 Status Register (Base Address + 0x08)                                      |     |

| 3.2.4 Interrupt Priority Vector Status/Clear Register (Base Address + 0x0C)      | 3-6 |

| 3.2.5 Interrupt Status/Clear Register (Base Address + 0x10)                      | 3-6 |

| 3.2.6 Interrupt Pending/Set Register (Base Address + 0x14)                       |     |

| 3.2.7 Generate Soft Interrupt Value Register (Base Address + 0x18)               |     |

| 3.2.8 Tx Address Overlay Control Register (Base Address + 0x1c)                  |     |

| 3.2.9 Rx Address Selector Control (Base Address + 0x2c)                          |     |

| 3.2.10 Rx Address PrivID Index (Base Address + 0x30)                             |     |

| 3.2.11 Rx Address PrivID Value Register (Base Address + 0x34)                    |     |

| 3.2.12 Rx Address Segment Index Register (Base Address + 0x38)                   |     |

| 3.2.13 Rx Address Segment Value Register (Base Address + 0x3c)                   |     |

| 3.2.14 Chip Version Register (Base Address + 0x40)                               |     |

| 3.2.15 Lane Power Management Control Register (Base Address + 0x44)              |     |

| 3.2.16 Rx Priority Control (Base Address + 0x48)                                 |     |

| 3.2.17 ECC Error Counters Register (Base Address + 0x4c)                         |     |

| 3.2.18 Link Status Register (Base Address + 0x58)                                |     |

| 3.2.19 Side Band State (Base Address + 0x5C).                                    |     |

| 3.2.20 Interrupt Control Index (Base Address + 0x60)                             |     |

| 3.2.21 Interrupt Control Value (Base Address + 0x64)                             |     |

| 3.2.22 Interrupt Pointer Index (Base Address + 0x68)                             |     |

| 3.2.23 Interrupt Pointer Value (Base Address + 0x6c)                             |     |

| 3.2.24 SerDes Control and Status 1 Register (Base Address + 0x70)                |     |

| 3.2.25 SerDes Control and Status 2 Register (Base Address + 0x74)                |     |

| 3.2.27 SerDes Control and Status 5 Register (Base Address + 0x76)                |     |

| 3.3 Remote HyperLink Configuration Registers                                     |     |

|                                                                                  |     |

| 3.4 HyperLink SerDes Configuration and Status Registers                          |     |

| 3.4.1 HyperLink SerDes Status Register (HYPERLINK_SERDES_STS)                    |     |

| 3.4.2 HyperLink SerDes PLL Configuration Register (HYPERLINK_SERDES_CFGPLL)      |     |

| 3.4.3 HyperLink SerDes Receive Configuration Register (HYPERLINK_SERDES_CFGRXn)  |     |

| 3.4.4 HyperLink SerDes Transmit Configuration Register (HYPERLINK_SERDES_CFGTXn) |     |

# Appendix A

| HyperLink SerDes Programming Examples     | A-1 |

|-------------------------------------------|-----|

| A.1 KeyStone I Device SerDes Programming  | A-2 |

| A.2 KeyStone II Device SerDes Programming | A-3 |

IX-1

# **List of Tables**

| Table 2-1  | HyperLink Pin Description                                          | 2-2  |

|------------|--------------------------------------------------------------------|------|

| Table 2-2  | Power Management Message                                           | 2-4  |

| Table 2-3  | Flow Control Message                                               | 2-4  |

| Table 2-4  | PLL Loop Bandwidth Selection                                       | 2-9  |

| Table 2-5  | Effect of the RATE Bits                                            | 2-9  |

| Table 2-6  | Example Operating Rate Configurations                              | 2-10 |

| Table 2-7  | Control Word Encoding                                              | 2-17 |

| Table 2-8  | Example of Address Translation                                     | 2-22 |

| Table 3-1  | Register Map                                                       | 3-2  |

| Table 3-2  | Revision Register Field Descriptions                               | 3-4  |

| Table 3-3  | Control Register Field Descriptions                                | 3-4  |

| Table 3-4  | Status Register Field Descriptions                                 | 3-5  |

| Table 3-5  | Interrupt Priority Vector Status/Clear Register Field Descriptions | 3-6  |

| Table 3-6  | Interrupt Status/Clear Register Field Descriptions                 | 3-7  |

| Table 3-7  | Interrupt Pending/Set Register Field Descriptions                  | 3-7  |

| Table 3-8  | Generate Soft Interrupt Value Register Field Descriptions          | 3-7  |

| Table 3-9  | TX Address Overlay Control Register Field Descriptions             | 3-8  |

| Table 3-10 | RX Address Selector Control Register Field Descriptions            |      |

| Table 3-11 | Rx Address PrivID Index Register Field Descriptions                | 3-12 |

| Table 3-12 | Rx Address PrivID Value Register Field Descriptions                | 3-12 |

| Table 3-13 | RX Address Segment Index Register Field Descriptions               | 3-12 |

| Table 3-14 | Rx Address Segment Value Register Field Descriptions               | 3-13 |

| Table 3-15 | Chip Version Register Field Descriptions                           | 3-14 |

| Table 3-16 | Lane Power Management Register Field Descriptions                  | 3-14 |

| Table 3-17 | Rx Priority Control Field Descriptions                             | 3-15 |

| Table 3-18 | ECC Error Counters Field Descriptions                              | 3-16 |

| Table 3-19 | Link Status Field Descriptions                                     | 3-17 |

| Table 3-20 | Side Band State Field Descriptions                                 | 3-17 |

| Table 3-21 | Interrupt Control Index Field Descriptions                         | 3-18 |

| Table 3-22 | Interrupt Control Value Field Descriptions                         | 3-19 |

| Table 3-23 | Interrupt Pointer Index Field Descriptions                         | 3-19 |

| Table 3-24 | Interrupt Pointer Value Field Descriptions                         |      |

| Table 3-25 | SerDes Control and Status 1 Register Field Descriptions            |      |

| Table 3-26 | SerDes Control and Status 2 Register Field Descriptions.           | 3-21 |

| Table 3-27 | SerDes Control and Status 3 Register Field Descriptions            | 3-21 |

| Table 3-28 | SerDes Control and Status 4 Register Field Descriptions            | 3-22 |

| Table 3-29 | KeyStone I HyperLink SerDes Configuration and Status Registers.    | 3-23 |

| Table 3-30 | HyperLink SerDes Status Register Field Descriptions                | 3-24 |

| Table 3-31 | HyperLink SerDes PLL Configuration Register Field Descriptions     | 3-25 |

| Table 3-32 | HyperLink SerDes RX Configuration Register n Field Descriptions    | 3-26 |

| Table 3-33 | HyperLink SerDes TX Configuration Register n Field Descriptions    | 3-28 |

| Table 3-34 | SerDes Transmit Configuration Post-Cursor Tap Weights (TWPST1)     | 3-29 |

|            |                                                                    |      |

# List of Figures

| Figure 1-1                 | Block Diagram.                                                                   |      |

|----------------------------|----------------------------------------------------------------------------------|------|

| Figure 1-2                 | MAC and PLS Operation                                                            |      |

| Figure 1-3                 | Point-to-Point Connection Through HyperLink                                      |      |

| Figure 2-1                 | HyperLink Connection                                                             |      |

| Figure 2-2                 | Station Management Interface Timing                                              |      |

| Figure 2-3                 | Lane 0 Power Up Timing                                                           |      |

| Figure 2-4                 | Timing Waveform for Second and Higher Lane Power Up.                             |      |

| Figure 2-5                 | Power State Transition (assuming quadlane, singlelane, and zerolane are all set) |      |

| Figure 2-6                 | HyperLink Write Operations                                                       |      |

| Figure 2-7                 | HyperLink Read Operations.                                                       |      |

| Figure 2-8                 | Control Word for Read and Write.                                                 |      |

| Figure 2-9                 | Control Word for Read Return.                                                    |      |

| Figure 2-10                | Control Word for Interrupt Packet                                                |      |

| Figure 2-11                | Address Translation in HyperLink                                                 |      |

| Figure 2-12                | Memory Map Example                                                               |      |

| Figure 2-13                | Address Translation at RX Side                                                   |      |

| Figure 2-14                | Interrupt Architecture in HyperLink                                              |      |

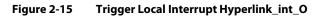

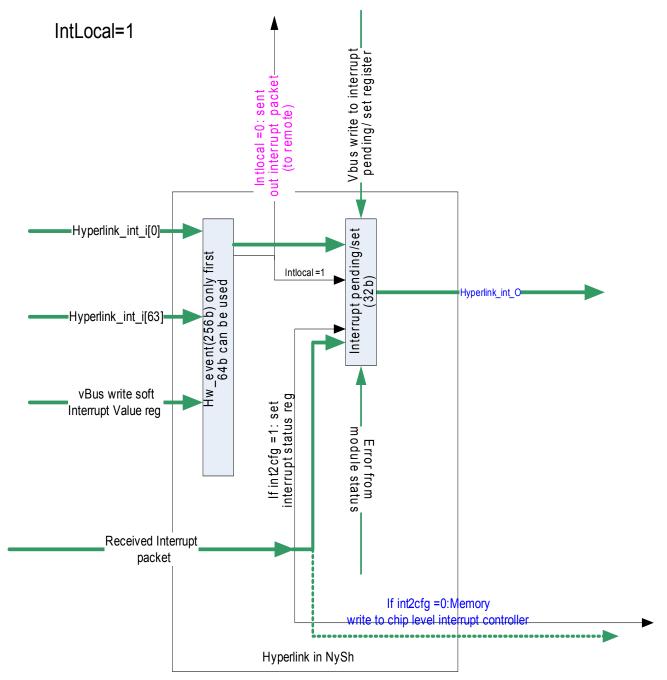

| Figure 2-15                | Trigger Local Interrupt Hyperlink_int_O                                          |      |

| Figure 2-16                | Interrupt Remote Device Through HyperLink                                        | 2-30 |

| Figure 3-1                 | Revision Register                                                                |      |

| Figure 3-2                 | Control Register                                                                 | 3-4  |

| Figure 3-3                 | Status Register                                                                  | 3-5  |

| Figure 3-4                 | Interrupt Priority Vector Status/Clear Register                                  | 3-6  |

| Figure 3-5                 | Interrupt Status/Clear Register                                                  | 3-6  |

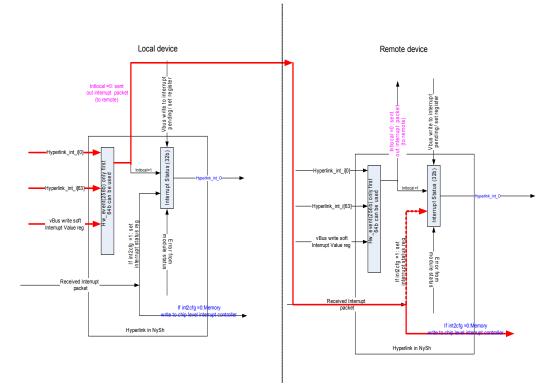

| Figure 3-6                 | Interrupt Pending/Set Register                                                   | 3-7  |

| Figure 3-7                 | Generate Soft Interrupt Value Register                                           | 3-7  |

| Figure 3-8                 | Tx Address Overlay Control Register                                              | 3-8  |

| Figure 3-9                 | Rx Address Selector Control Register                                             | 3-9  |

| Figure 3-10                | Rx Address PrivID Index Register                                                 | 3-12 |

| Figure 3-11                | Rx Address PrivID Value Register                                                 | 3-12 |

| Figure 3-12                | Rx Address Segment Index Register                                                | 3-12 |

| Figure 3-13                | Rx Address Segment Value Register                                                | 3-13 |

| Figure 3-14                | Chip Version Register                                                            |      |

| Figure 3-15                | Lane Power Management Register                                                   |      |

| Figure 3-16                | Rx Priority Control                                                              |      |

| Figure 3-17                | ECC Error Counters                                                               |      |

| Figure 3-18                | Link Status                                                                      |      |

| Figure 3-19                | Side Band State                                                                  |      |

| Figure 3-20                | Interrupt Control Index                                                          |      |

| Figure 3-21                | Interrupt Control Value                                                          |      |

| Figure 3-22                | Interrupt Pointer Index                                                          |      |

| Figure 3-23                | Interrupt Pointer Value                                                          |      |

| Figure 3-24                | SerDes Control and Status 1 Register                                             |      |

| Figure 3-25                | SerDes Control and Status 2 Register                                             |      |

| Figure 3-26                | Figure 2-25 SerDes Control and Status 3 Register                                 |      |

| Figure 3-20                | Figure 2-26 SerDes Control and Status 5 Register                                 |      |

| Figure 3-27<br>Figure 3-28 | HyperLink SerDes Status Register                                                 |      |

| Figure 3-28<br>Figure 3-29 | HyperLink SerDes PLL Configuration Register                                      |      |

| Figure 3-29<br>Figure 3-30 | HyperLink SerDes RX Configuration Register n                                     |      |

| -                          |                                                                                  |      |

| Figure 3-31                | HyperLink SerDes TX Configuration Register n                                     |      |

www.ti.com

# Preface

## **About This Manual**

HyperLink provides a high-speed, low-latency, and low-pin-count communication interface that extends the internal CBA 3.x-based transactions between two KeyStone devices.

# **Notational Conventions**

This document uses the following conventions:

- Commands and keywords are in **boldface** font.

- Arguments for which you supply values are in *italic* font.

- Terminal sessions and information the system displays are in screen font.

- Information you must enter is in **boldface screen font**.

- Elements in square brackets ([]) are optional.

Notes use the following conventions:

**Note**—Means reader take note. Notes contain helpful suggestions or references to material not covered in the publication.

The information in a caution or a warning is provided for your protection. Please read each caution and warning carefully.

**CAUTION**—Indicates the possibility of service interruption if precautions are not taken.

**WARNING**—Indicates the possibility of damage to equipment if precautions are not taken.

Preface

# **Related Documentation from Texas Instruments**

| C66x CorePac User Guide                                                 | SPRUGW0 |

|-------------------------------------------------------------------------|---------|

| Enhanced Direct Memory Access 3 (EDMA3) for KeyStone Devices User Guide | SPRUGS5 |

| Chip Interrupt Controller (CIC) for KeyStone Devices User Guide         | SPRUGW4 |

| Memory Protection Unit (MPU) for KeyStone Devices User Guide            | SPRUGW5 |

| Multicore Navigator for KeyStone Devices User Guide                     | SPRUGR9 |

| Phase Locked Loop (PLL) Controller for KeyStone Devices User Guide      | SPRUGV2 |

| Power Management for KeyStone Devices                                   | SPRABHO |

| Power Sleep Controller (PSC) for KeyStone Devices User Guide            | SPRUGV4 |

|                                                                         |         |

# Trademarks

C6000 is a trademark of Texas Instruments Incorporated.

All other brand names and trademarks mentioned in this document are the property of Texas Instruments Incorporated or their respective owners, as applicable.

# Chapter 1

# Introduction

- 1.1 "Purpose of HyperLink" on page 1-2

- 1.2 "Terminology Used in This Document" on page 1-2

- 1.3 "Features" on page 1-2

- 1.4 "Functional Block Diagram" on page 1-4

- 1.5 "Supported Use Case Statement" on page 1-6

- 1.6 "Industry Standard(s) Compliance Statement" on page 1-6

# 1.1 Purpose of HyperLink

HyperLink provides a high-speed, low-latency, and low-pin-count communication interface that extends the internal CBA 3.x-based transactions between two KeyStone devices. It can emulate all currently-used peripheral interface mechanisms. HyperLink includes the data signals and the sideband control signals. The data signals are SerDes-based and the sideband control signals are LVCMOS-based. The current version of HyperLink offers point-to-point connection between two devices.

# **1.2 Terminology Used in This Document**

| Term   | Definition                                          |

|--------|-----------------------------------------------------|

| СВА    | Common Bus Architecture                             |

| LVCMOS | Low Voltage Complementary Metal Oxide Semiconductor |

| QM     | Queue Manager                                       |

| SerDes | Serializer/Deserializer                             |

# **1.3 Features**

The HyperLink module has the following features:

- Low pin count (as few as 26 pins)

- SerDes for data transfer

- LVCMOS sideband signals dedicated for control

- No Tri-State Signals

- All signals are dedicated and driven by only one device

- All LVCMOS sideband signals are driven using source synchronous clocking

- Up to 12.5 Gbaud rate per lane, 1 or 4 lanes for Tx and Rx data

- Support SerDes full, half, quarter and eighth rates for slower speeds

- Auto SerDes polarity detection and correction

- Auto SerDes lane identification and correction

- Simple packet-based transfer protocol for memory-mapped access

- Write Request/Data Packet

- Read-request packet

- Read-response data packet

- Interrupt-request packet

- Supports multiple outstanding transactions

- Point-to-point connection

- Request packets and response packets are multiplexed through the same physical pins

- Supports both host/peripheral and peer-to-peer communication models

- Dedicated LVCMOS pins for flow control and power management

- Supports per-direction, per-channel flow control

- Supports per-lane, per-direction power management

- Automatically adjusts lane width for power saving

- Internal SerDes loopback mode for diagnostics

- Requires no external pull-up or pull-down resistors

- 64 interrupt inputs for both hardware and software

- Eight interrupt-pointer addresses

- Does not support write-response packets

- Both TX and RX SerDes must run at the same speed

- Extended control word for commands not used in this version

- Maximum burst size supported to access remote registers is 64 bytes. Bursts greater than 64B may cause CBA violations.

- No exclusive transport operation supported

- CBA constant mode is not supported for bursts larger than 256-byte aligned burst

# 1.4 Functional Block Diagram

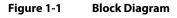

Figure 1-1 shows the internal modules of the HyperLink block.

The HyperLink module implements two 256-bit, VBUSM interfaces. The slave interface is required for transmit and control register access and the master interface is required for receive. Transmit and Receive state machine blocks convert to/from the 256-bit CBA bus to the external serial interface.

There are address transaction blocks at the ingress and egress sides. The egress address combines the various characteristics of the CBA transactions the HyperLink slave port receives—such as security features, privID information, and memory-mapped addresses—into the outgoing address. On the ingress side, the HyperLink takes the address fields and remaps them into a CBA transaction. The address translations for ingress and egress are done independently and, therefore, controlled by different sets of registers to increase processing flexibility and scalability.

Because HyperLink logic and SerDes may run different clocks, multiple FIFOs are added to buffer the entire data burst and multiple commands. Ingress and egress have their own FIFOs, as does the read-return data for ingress and egress.

The station management block processes the power management and flow control sideband signals, such as power a lane up/down, flow control, enable/disable TX/RX transceiver, etc. The station management is also used for initialization and error recovery.

The PLS module on the egress side encodes the MAC transmit data using a GFP 32/33 encoding, adding a nine-bit Error Correction Code (ECC), then scrambling the data before sending it to the SerDes. On the ingress side, the PLS aligns the serial bit stream to the 36-bit symbol boundary, identifies the synchronizing codes, descrambles the data, aligns to the ECC boundary, performs the ECC correction, decodes data using GFP 33/32, and presents the resulting data to the MAC receiver.

When a command arrives at the slave interface for remote destination, a 64- or 128-bit command is written to the FIFO followed by any applicable data. Data is written in 8-, 16-, 24-, or 32-byte octet-aligned quanta. That is, the smallest write is eight bytes. The FIFO can accept up to 32 bytes of data per bus clock.

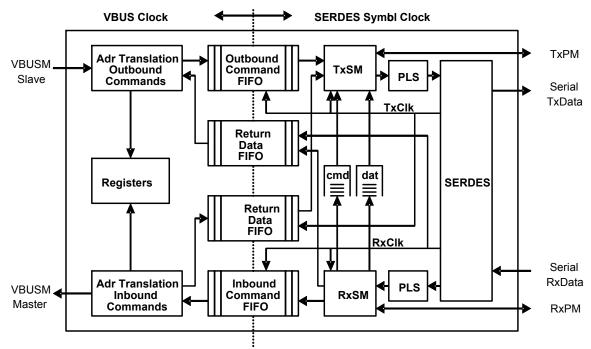

Figure 1-2 shows the flow of data from the FIFOs through the MAC and PLS to the wire.

- Step A: Takes up to 128 bits of data and associated byte enables (two-frame quanta) from the FIFO and slices it into 32-bit quanta with 4-bit byte enables. This results in 144 bits of information.

- Step B: Encodes the 32 bits of data and associated byte enables using a GFP encoding into 33 bits. This results in 132 bits of information.

- Step C: Takes four GFP encoded data words and adds the associated MAC last flags and a sync bit, calculates the ECC, and adds the nine bits of ECC to the word. This results in 144 bits of information.

- Step D: Splits the 144-bit word into four 36-bit lane data elements.

- Step E: Scrambles each lane to remove any repeating patterns that could cause a receive-recovery error.

#### Figure 1-2 MAC and PLS Operation

www.ti.com

# **1.5 Supported Use Case Statement**

HyperLink offers a packet-based transfer protocol and supports multiple outstanding read, write, and interrupt transactions. It can run in one-lane or four-lanes mode with each lane running at 12.5Gbaud rate. HyperLink uses an efficient encoding scheme for the physical layer. Compared to the traditional 8b10b encoding scheme for high speed interfaces, HyperLink reduces the encoding overhead; the efficient encoding scheme in HyperLink is equivalent to 8b9b.

The sideband signals provide the flow control and power management control information. After configuration, HyperLink has internal state machines to automatically manage the flow control and power saving based on the sideband signals without any software intervention. Flow control is managed independently on a per-direction basis. The RX side sends the throttle signals to the TX side. On the other hand, the power management is controlled by the TX side. In addition, power management is controlled on a per-direction basis.

HyperLink is not compatible with VLYNQ due to the SerDes interface signaling.

# 1.6 Industry Standard(s) Compliance Statement

The HyperLink is a TI-specific peripheral. There is no industry standard for it.

# Chapter 2

# Architecture

- 2.1 "Clock Control" on page 2-2

- 2.2 "Memory Map" on page 2-2

- 2.3 "Signal Descriptions" on page 2-2

- 2.4 "Pin Multiplexing" on page 2-3

- 2.5 "Station Management Interface" on page 2-3

- 2.6 "SerDes Configuration and Clocking" on page 2-8

- 2.7 "HyperLink Protocol" on page 2-12

- 2.8 "Passing an Interrupt to a Remote Device" on page 2-30

- 2.9 "Reset Considerations" on page 2-31

- 2.10 "Initialization" on page 2-31

- 2.11 "DMA Event Support" on page 2-31

- 2.12 "Power Management" on page 2-31

- 2.13 "Emulation Considerations" on page 2-31

# 2.1 Clock Control

HyperLink needs a reference clock for its SerDes module. The reference clock can be of the following frequencies:

- 156.25 Mhz

- 250 MHz

- 312 MHz

# 2.2 Memory Map

Not applicable.

Г

# 2.3 Signal Descriptions

This section describes each of the signals on the external interface and their functions.

HyperLink includes both SerDes pins and LVCMOS pins. The SerDes pins are for data transfer and the LVCMOS pins are sideband signals for control, such as flow control and power management.

Table 2-1HyperLink Pin Description

| Pin Name       | Pin Count | Туре | Гуре Function                                                  |  |  |  |  |

|----------------|-----------|------|----------------------------------------------------------------|--|--|--|--|

| LVCMOS Pins    |           |      |                                                                |  |  |  |  |

| TXPM_CLK_O     | 2         | Out  | Clock for transmit Power Management Output two wire bus        |  |  |  |  |

| TXPM_DAT_O     | 2         | Out  | Transmit Power Management Output two wire bus                  |  |  |  |  |

| TXFL_CLK_I     | 2         | In   | Clock for transmit Flow Management Input two wire bus          |  |  |  |  |

| TXFL_DAT_I     | 2         | In   | Transmit Flow Management Input two wire bus                    |  |  |  |  |

| RXPM_CLK_I     | 2         | In   | Received clock for receive Power Management Input two wire bus |  |  |  |  |

| RXPM_DAT_I     | 2         | In   | Receive Power Management Input two wire bus                    |  |  |  |  |

| RXFL_CLK_O     | 2         | Out  | Clock for receive Flow Management Output two wire bus          |  |  |  |  |

| RXFL_DAT_O     | 2         | Out  | Receive Flow Management Output two wire bus                    |  |  |  |  |

| SerDes Pins    |           |      |                                                                |  |  |  |  |

| SERDES_RXP0    | 1         | In   | Differential Rx pin lane 0 (Positive)                          |  |  |  |  |

| SERDES_RXN0    | 1         | In   | Differential Rx pin lane 0 (Negative)                          |  |  |  |  |

| SERDES_RXP1    | 1         | In   | Differential Rx pin lane 1(Positive)                           |  |  |  |  |

| SERDES_RXN1    | 1         | In   | Differential Rx pin lane 1 (Negative)                          |  |  |  |  |

| SERDES_RXP2    | 1         | In   | Differential Rx pin lane 2(Positive)                           |  |  |  |  |

| SERDES_RXN2    | 1         | In   | Differential Rx pin lane 2(Negative)                           |  |  |  |  |

| SERDES_RXP3    | 1         | In   | Differential Rx pin lane 3(Positive)                           |  |  |  |  |

| SERDES_RXN3    | 1         | In   | Differential Rx pin lane 3(Negative)                           |  |  |  |  |

| SERDES_REFCLKP | 1         | In   | SerDes Differential Reference Clock (Positive)                 |  |  |  |  |

| SERDES_REFCLKN | 1         | In   | SerDes Differential Reference Clock (Negative)                 |  |  |  |  |

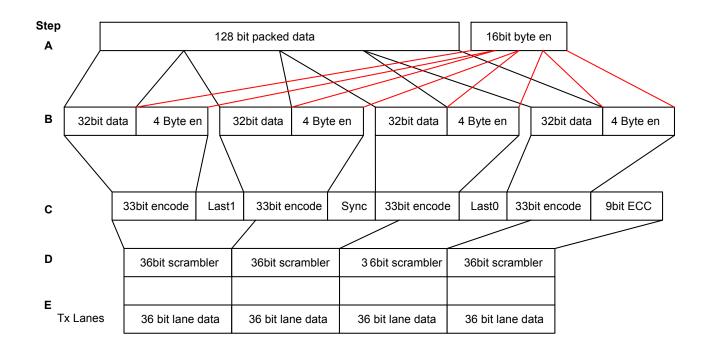

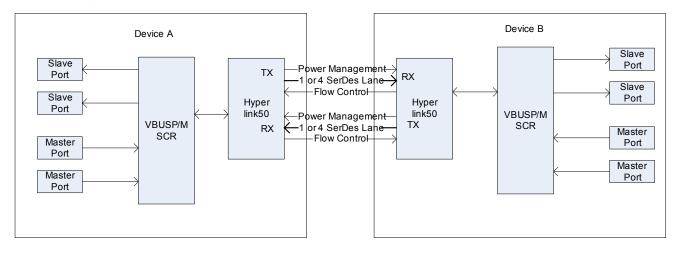

Figure 2-1 shows the connection between two devices through the HyperLink interface. Currently, HyperLink provides only point-to-point connections between two devices.

#### Figure 2-1 HyperLink Connection

# 2.4 Pin Multiplexing

There is no pin multiplexing for HyperLink.

## 2.5 Station Management Interface

The station management interface refers to the LVCMOS pins in HyperLink, which are used for flow control and power management for HyperLink. The HyperLink module uses the TXPM and TXFL station management busses to control the SerDes TXDATA serial interface; the RXPM and RXFL station management busses are used to control the SerDes RXDATA serial interface.

Both flow control and power management have dedicated interfaces for sideband events.

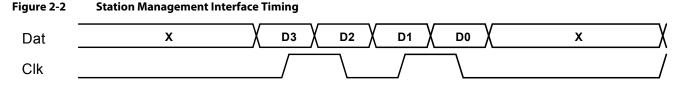

Each station management interface includes a data signal and clock. The data line carries a 4-bit value and is clocked by the receiver on each edge of the CLK signal. This methodology allows the clock and data to have the same maximum bandwidth, which enables the interface to potentially operate at higher rates for the same buffer type. The four-bit value in the data line supports up to 15 different messages which are sent MSB first. Message 0b1110 is used to transfer four bits of abilities followed by four bits of status. Bit 3 (MSB) of the status message is always zero to prevent the remote device from detecting a reset sequence.

To reset the station management bus, a sequence of eight 1s followed by four 0s is sent. Anytime the receiver of the station management bus sees more than seven 1s in a row, it resets its outputs to their default values and enters the sync state waiting for the four 0s. After the four 0s are received, the reset of the station management bus is complete.

When the station management bus is started, the transmit station management entity sends a reset sequence to the remote followed by a capabilities/status message. When a receive station management entity receives a reset sequence, it responds by sending a capabilities/status message; this allows either side of the link to start before the other and still determine remote capabilities. When both devices have received the capability/status message, the station management bus is considered linked and the capabilities are displayed in the status register.

The station management bus is clocked at one fourth the SerDes symbol rate or one fourth the VBUS\_CLK rate.

The following tables show the commands sent on the TXPM or received on the RXPM bus. The capabilities are sent anytime reset is removed or when a reset sequence is seen on the receiver.

| Table 2-2      | Power Management Message    |

|----------------|-----------------------------|

| D3D2D1D0       | Description                 |

| 0b0000         | Disable One Lane Receiver   |

| 0b0001         | Enable one lane Receiver    |

| 0b0010         | Disable Four Lane Receiver  |

| 0b0011         | Enable Four Lane Receiver   |

| 0b0010 to 0b11 | 01 Reserved                 |

| 0b1110         | Capabilities/Status Message |

| 0b1111         | Reserved for reset          |

| 1              |                             |

Table 2-2

Power Management Message

Table 2-3 shows the commands sent RXFL or received on TXFL bus. The capabilities are sent anytime reset is removed or when a reset sequence is seen on the receiver.

|                  | 5                           |

|------------------|-----------------------------|

| D3D2D1D0         | Description                 |

| 0b0000           | Channel 0 Operational       |

| 0b0001           | Channel 0 flow controlled   |

| 0b0010 to 0b0111 | Reserved                    |

| 0b1000           | Receive synch not locked    |

| 0b1001           | Receive sync locked         |

| 0b1010 to 0b1101 | Reserved for Future Use     |

| 0b1110           | Capabilities/Status Message |

| 0b1111           | Used for Reset              |

Table 2-3 Flow Control Message

Each capability message contains four bits: D3D2D1D0. Only two bits are currently used. The following lists how to decode the capability message:

- D0 =1 means the high speed above 12.5 GBaud, D0=0 means support 12.5 GBaud and below.

- D1=1 means support four lane, D1=0 means it does not support four lane mode.

- D2 and D3 are currently reserved, should be always zero.

#### 2.5.1 Lane Activation

To power up a lane, the transmitter informs the receiver of a power-up event through the TXPM. The receiver gets the power-up event through RXPM, then enables the receiver. When the receiver is fully synchronized with the transmitter training sequence, the receiver sends an event back to the transmitter to inform the transmitter that it can use the lane for data transfer. The receiver then detects the transition from the training sequence to the data receiving mode.

To support the symbol alignment within SerDes, an enable from the PLS needs to indicate to SerDes that symbol alignment can occur. The synchronization word described earlier contains a comma so that this can easily be done in SerDes. Each lane needs a symbol alignment and, depending on the state of the other lanes, phase correction may occur on all active lanes. This feature allows one operating lane to expand to four lanes without the need for the operating lane to be taken down during alignment with the other lanes.

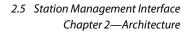

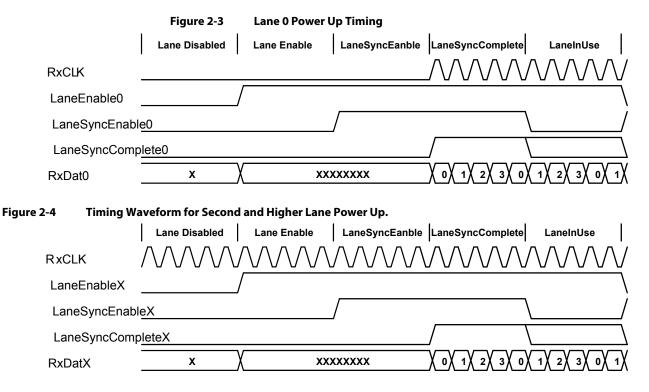

Figure 2-3 shows a high-level timing of lane 0 startup.

**Lane Disable**—The SerDes lane is in its lowest power state. If all lanes are disabled, the SerDes power should be as close to zero as possible.

**Lane Enable**—The SerDes lane is enabled and the receiver is passing data seen on the Rx pins to the PLS layer.

**LaneSyncEnable**—SerDes is looking for the comma characters and, once they are detected, will symbol-align the land. SerDes will then set the LansSyncComplete back to the PLS for completion of the activation process.

LaneInUse—SerDes is aligned to the 36-bit word boundary. It ignores any comma characters detected. The PLS receives the DataInUse indicator and starts using the lane.

#### 2.5.2 Flow Control

Flow control in the HyperLink module is transparent to the user. The RX side of HyperLink automatically manages the traffic flow based on available resources and throttles the TX side of traffic through the sideband signals.

#### 2.5.3 Power Management

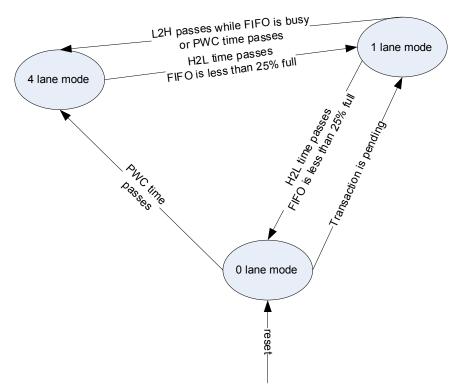

The HyperLink transmitter actively determines the power states it enters based on the Lane Power Management Register (see Table 3-16 on page 3-14) and informs its correspondent receivers on the other side through the sideband signals to enter the same power state.

During reset SerDes is held in a power down state with all lanes disabled. After exiting reset, the HyperLink module sends a message via the sideband bus to the remote device requesting its abilities. After the abilities are received, the HyperLink automatically enters an operable state. SerDes is only brought out of reset if either the zero lane bit of the PWRMGT register has been cleared or a transaction is pending. The HyperLink module automatically changes the power mode based on the PWRMGT register settings and the outbound load. By default, the HyperLink leaves the Tx link idle until a transaction is received from its VBUS slave port. Then, the HyperLink enters one lane mode to serve this transaction and the lane power up procedure for one lane is completed. HyperLink dynamically manages its power mode based on the traffic load. When a single lane can not keep up with the traffic load, the HyperLink module automatically enters the four-lane mode, if it is supported. If the load drops to below single-lane performance, the HyperLink module automatically enters the single lane mode by powering down the upper three lanes. If the traffic load is further reduced, the HyperLink automatically enters the zero-lane mode by disabling the single-lane mode and shutting down SerDes until it sees the next transaction. Both transmit and receive are independently controlled so that for certain applications only one direction may be needed.

The transition among different modes is controlled by the lane power management register (Section 3.2.15 "Lane Power Management Control Register (Base Address + 0x44)" on page 3-14).

#### Figure 2-5 Power State Transition (assuming quadlane, singlelane, and zerolane are all set)

# 2.6 SerDes Configuration and Clocking

This section describes the SerDes macro provided with the Keystone I HyperLink module.

**Note**—SerDes module information for KeyStone II devices is not provided in this user guide. Please check for availability of the SerDes User Guide for KeyStone II Devices on the device product page.

The SerDes macro controls the operating rate of the HyperLink, and provides an interface between the HyperLink module transmit and receive interfaces and the external device pins. This section discusses the following topics:

- HyperLink SerDes Operating Rate Configuration

- HyperLink SerDes Receive Interface

- HyperLink SerDes Transmit Interface

Each interface is discussed more detail in the subsequent sections. A set of chip-level registers are provided to access each interface. See the register chapter for more information about these registers. For example code showing how to configure the SerDes, see "HyperLink SerDes Programming Examples" on page A-1.

**Note**—The SerDes registers are provided at the chip level and are not located in the HyperLink configuration register space. Before accessing these registers, the Kick registers must be programmed to allow access to this register space. See the device-specific data manual for the address of the HyperLink SerDes registers.

#### 2.6.1 HyperLink SerDes Operating Rate Configuration

This section describes how to configure the HyperLink SerDes operating rate. The operating rate of the HyperLink SerDes depends on the configuration of the HyperLink SerDes PLL and the rate scaling factor (RATESCALE) of the receiver and the transmitter. This section also provides information about how to configure the HyperLink SerDes PLL loop bandwidth.

The main purpose of the HyperLink SerDes PLL is to generate a high frequency output clock from a low frequency reference clock (REFCLK). The PLL output frequency depends on the MPY field in HYPERLINK\_SERDES\_CFGPLL chip-level register, and is calculated by the following equation:

PLL\_OUTPUT=REFCLK\*MPY

The MPY field can be programmed to several values; however, the PLL\_OUTPUT value must be in the 1.5625 GHz to 3.125 GHz range.

Because the PLL uses the low frequency REFCLK input to generate the high frequency output clock, any jitter in the REFCLK can be amplified in the PLL\_OUT. If there is too much jitter, it can affect the ability of the transmitter and the receiver to work correctly. To help minimize the effect of the jitter, the LOOP\_BANDWIDTH setting is provided. The LOOP\_BANDWIDTH field has four settings; a setting that provides a PLL bandwidth in the 8-30 MHz range must be chosen. The PLL bandwidth is defined by the following equation:

PLL\_BANDWIDTH = REFCLK/BWSCALE

Table 2-4 shows the BWSCALE values that correspond to different combinations of PLL\_OUTPUT frequency and LOOP\_BANDWIDTH. Medium bandwidth typically provides the best results, so begin by calculating the PLL\_BANDWIDTH using the medium bandwidth BWSCALE for your PLL\_OUTPUT frequency. If the PLL\_BANDWIDTH for the medium bandwidth configuration is in the 8-30 MHz range, then use the medium bandwidth setting. If the medium bandwidth setting provides a PLL\_BANDWIDTH outside the 8-30 MHz range, then repeat the PLL\_BANDWIDTH calculation with other LOOP\_BANDWIDTH settings to find one that yields a result in the 8-30 MHz range.

| PLL_OUTPUT Frequency (GHz) | LOOP_BANDWIDTH       | BWSCALE | PLL_BANDWIDTH           |

|----------------------------|----------------------|---------|-------------------------|

|                            | Medium Bandwidth     | 13      | PLL_BANDWIDTH=REFCLK/13 |

| 3.125                      | Low Bandwidth        | 21      | PLL_BANDWIDTH=REFCLK/21 |

| 5.125                      | Ultra High Bandwidth | 7       | PLL_BANDWIDTH=REFCLK/7  |

|                            | High Bandwidth       | 10      | PLL_BANDWIDTH=REFCLK/10 |

|                            | Medium Bandwidth     | 14      | PLL_BANDWIDTH=REFCLK/14 |

| 21                         | Low Bandwidth        | 8       | PLL_BANDWIDTH=REFCLK/8  |

| 2.1                        | Ultra High Bandwidth | 23      | PLL_BANDWIDTH=REFCLK/23 |

|                            | High Bandwidth       | 11      | PLL_BANDWIDTH=REFCLK/11 |

|                            | Medium Bandwidth     | 16      | PLL_BANDWIDTH=REFCLK/16 |

| 1 5 6 2 5                  | Low Bandwidth        | 8       | PLL_BANDWIDTH=REFCLK/8  |

| 1.5625                     | Ultra High Bandwidth | 30      | PLL_BANDWIDTH=REFCLK/31 |

|                            | High Bandwidth       | 14      | PLL_BANDWIDTH=REFCLK/14 |

| End of Table 2-4           |                      |         |                         |

Table 2-4

PLL Loop Bandwidth Selection

The RATE field in the receive and transmit interfaces provides an additional level of scaling beyond what is provided by the PLL (see the HYPERLINK\_SERDES\_CFGRX and HYPERLINK\_SERDES\_CFGTX registers for more information). The RATE field allows 4 different rates to be selected, which can increase or decrease the operating rate of the HyperLink. The transmit and receive rate must be consistent between the transmitter and receiver (e.g. they must be operating at the same rate). The effect of the rate scale factors are shown in table Table 2-5.

| Rate         | RATESCALE | Description                                             |

|--------------|-----------|---------------------------------------------------------|

| Full Rate    | 0.25      | Four data samples taken per PLL output clock cycle      |

| Half Rate    | 0.5       | Two data sample taken per PLL output clock cycle        |

| Quarter Rate | 1         | One data sample taken per PLL output clock cycle        |

| Eighth Rate  | 2         | One data sample taken every two PLL output clock cycles |

Using the below equation, the operating rate, or LINERATE, of the HyperLink SerDes can be calculated using the REFCLK, the MPY factor, and the RATESCALE.

LINERATE=REFCLK\*MPY/RATESCALE

Using the maximum frequency of REFCLK\*MPY=3.125, and the maximum RATESCALE (full rate), the maximum LINERATE of the HyperLink module is:

#### LINERATE=3.125/0.25= 12.5 GHz

Table 2-6 shows several example operating rates for different combinations of REFCLK, MPY, and RATE values. Please see the device specific data manual for the REFCLK frequencies supported by the HyperLink module.

Table 2-6

Example Operating Rate Configurations

|              |                  | LINERATE=REFCLK*MPY/RATESCALE (GHz) |                              |                             |                              |  |  |  |  |

|--------------|------------------|-------------------------------------|------------------------------|-----------------------------|------------------------------|--|--|--|--|

| RefClk (MHz) | MPY              | Eighth (11b)<br>RATESCALE=2         | Quarter (10b)<br>RATESCALE=1 | Half (01b)<br>RATESCALE=0.5 | Full (00b)<br>RATESCALE=0.25 |  |  |  |  |

|              | 16 (0100000b)    | 1.25                                | x                            | x                           | х                            |  |  |  |  |

| 156.25       | 10 (00101000b)   | х                                   | x                            | 3.125                       | 6.25                         |  |  |  |  |

|              | 20 (01010000b)   | х                                   | x                            | x                           | 12.5                         |  |  |  |  |

| 250          | 10 (00101000b)   | 1.25                                | x                            | x                           | x                            |  |  |  |  |

|              | 12.5 (00110010b) | х                                   | 3.125                        | 6.25                        | 12.5                         |  |  |  |  |

|              | 8 (0010000b)     | 1.25                                | x                            | x                           | x                            |  |  |  |  |

| 312.5        | 5 (00010100b)    | х                                   | x                            | 3.125                       | 6.25                         |  |  |  |  |

|              | 10 (00101000b)   | х                                   | x                            | x                           | 12.5                         |  |  |  |  |

The PLL is enabled automatically by the HyperLink module, based on the value of the RESET bit in the CONTROL register. When enabled, the user must poll the LOCK bit in the HYPERLINK\_SERDES\_STS to ensure that the PLL is operating properly.

#### 2.6.2 HyperLink SerDes Receive Interface

This section discusses the HyperLink SerDes receive interface. The receive interface consists of four data lanes, each of which is configured through the HYPERLINK\_SERDES\_CFGRX[3-0] chip level registers. The ENRX field in these registers provide the status of the receive modules. The receive modules are enabled automatically by the HyperLink module.

The main task of the receiver is to perform data/clock recovery on the receive signals. The clock recovery algorithms are controlled by the CDR field in the HYPERLINK\_SERDES\_CFGRXn register. The clock data recover algorithms operate to adjust the clocks used to sample RXp and RXn so that the data samples are taken midway between data transitions. Both first and second order algorithms are provided, and both algorithms use the same basic technique for determining whether the sampling clock is ideally placed, or if it needs to be moved earlier or later.

The first order algorithm operates by making a single phase adjustment each time a threshold is equalled or exceeded. The second order algorithm acts repeatedly according to the net difference between the number of times the selected first order threshold is equalled or exceeded, thereby adjusting for the rate of change of phase.

For each algorithm, there are several phase tracking rates that can be configured to adjust the tracking rate that is used for that algorithm. Although higher order algorithms and higher tracking rates provide better precision, they are cause higher power consumption. If power consumption is a concern, then selecting a lower order algorithm or a lower tracking rate can save power at the expense of phase tracking. The algorithm and tracking rate that provides the best results for phase tracking and power consumption must be evaluated for each system.

The receiver also supports the ability to detect a loss of signal condition, also known as electrical idle. Loss of signal detection can be enabled through the LOS field in the HYPERLINK\_SERDES\_CFGRXn register. When loss of signal detection is enabled, the LOSDTCT bit in the HYPERLINK\_SERDES\_STS register can be used to monitor whether a loss of signal condition has occurred.

# 2.6.3 HyperLink SerDes Transmit Interface

This section discusses the HyperLink SerDes transmit interface. The transmit interface consists of 4 data lanes, each of which is configured through the HYPERLINK\_SERDES\_CFGTX[3-0] chip level registers. The ENTX field in these registers provide the status of the transmit modules. The transmit modules are enabled automatically by the HyperLink module.

The transmit interface sets up the transmit lanes, and provides options for signal conditioning on the transmit signals. Please see the SWING, TWPRE, and TWPST1 fields in HYPERLINK\_SERDES\_CFGTXn registers for more information about the configuration options for the transmitter.

## 2.6.4 HyperLink SerDes Training Process

The Hyperlink peripheral is designed to initialize itself and its remote link partner with minimal CPU intervention. The Hyperlink peripheral will start its side-band signal and SERDES training sequence as soon as it detects the SERDES PLL has achieved lock status (HYPLINK\_SERDES\_STS[0] = 1).

The PLL enable signal of the Hyperlink SERDES module is tied to the Hyperlink module reset signal. Because of this, when the Hyperlink peripheral comes out of reset the PLL enable bit in HYPLINK\_SERDES\_CFGPLL register is set internally.

Because the PLL enable bit is set as reset is de-asserted, when a non-zero MPY value is written to the HYPLINK\_SERDES\_CFGPLL register the SERDES PLL will lock and the Hyperlink training sequence will be triggered.

To ensure that the Hyperlink configuration registers are properly utilized during the initial training sequence, and to ensure robust communication both during the training sequence and in subsequence data traffic, the following sequence of steps should be followed for Hyperlink peripheral initialization.

- 1. The Hyperlink peripheral is released from reset after normal reset sequence is completed

- 2. System should assure that both Hyperlink link devices are out of reset and running application code

- 3. Application should then configure any general Hyperlink registers and Configure the SerDes transmitter and receiver configuration registers

- 4. The application should then program the PLL configuration register with the proper MPY settings. If the settings are valid, this will result in the PLL locking to the given reference clock at the designated output frequency setting

- 5. Hyperlink will wait for SerDes PLL lock and then start the Hyperlink side-band signal and SerDes training sequence

In addition to the proper initialization sequence, there are initial analog effects of the SerDes transmitters and receivers that must be accounted for when the Hyperlink SerDes training sequence turns the SerDes transmitters and receivers on for the first time after a power-on-reset state or when coming out of a Hyperlink sleep mode.

The Hyperlink SerDes Control and Status 1 Register (SDCS1) at Hyperlink memory map offset 0x70 contains two bit fields that allow for a controlled number of initial SERDES symbols to be masked by the SerDes receivers during initial SerDes power up or when coming out of a Hyperlink sleep state.

SDCS1[sleep\_cnt] control the amount of SerDes symbols that are masked for lanes that enter a sleep/enable state. This allows the internal SerDes power supplies to stabilize before the link is established.

SDCS1[disable\_cnt] controls the amount of SerDes symbols that are masked for a SERDES lane that enters a disabled state. This allows the SerDes clock data recovery (CDR) and equalizer to stabilize before the link is established.

Sleep masked symbol count = sleep\_cnt x 16 x Unit Interval

Disable masked symbol count = disable\_cnt x 16 x Unit Interval

Unit Interval is the bit-period width of the SerDes symbol as determined by the PLL and transmitter settings.

The recommended value for SDCS1[sleep\_cnt] is 0xFF. Likewise the recommended value for SDCS1[disable\_cnt] is 0xFF. This setting will provide the SerDes transmitters and receivers the maximum amount of time to stabilize after initial power on and after exiting a sleep state.

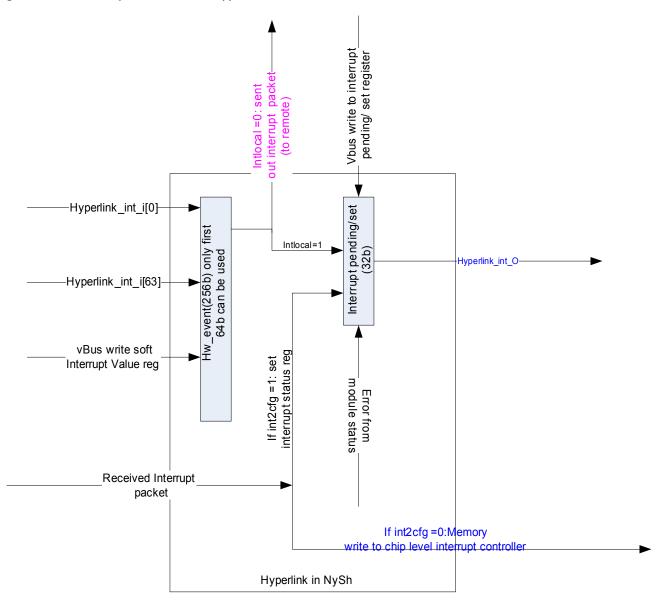

## 2.7 HyperLink Protocol

HyperLink provides three types of transactions: read, write, and interrupt events. The following section describes the data flow for read and write operations. The interrupt event is carried by a special packet format. See Section 2.7.5 "Interrupt" on page 2-24 for more information about the interrupt capability of HyperLink.

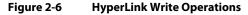

#### 2.7.1 HyperLink Write Operations

This section discusses the HyperLink write operations. The write process is outlined in Procedure 2-1 and shown in Figure 2-6.

#### Procedure 2-1 HyperLink Write Operation

#### Step - Action

- I HyperLink receives a write transaction from its slave VBUSM port, and the write command is written to Outbound Command FIFO.

- 2 Data is subsequently read from the FIFO and encapsulated in a Write Request packet.

- 3 The egress address transaction logic overlay controls information into address field.

- 4 The packet is encoded and serialized before being transmitted to the remote device.

- 5 The remote device receives the packet, deserializes, and decodes the receive data.

- **6** The remote HyperLink module stores the received write packet into the Inbound Command FIFO.

- 7 The ingress address translation logic generates the new memory-mapped address and other control information such as security and PRIVID for the write transaction.

- 8 The HyperLink in the remote device initiates a VBUSM master write operation based on the new address and other control information generated by the ingress address transaction

- **9** The write data lands at the remote device.

- **10** For a burst write larger than 256B, the write operation is divided into multiple bursts with the maximum burst size of 256B at the remote device. Step 2 to step 9 are repeated for each burst of write data.

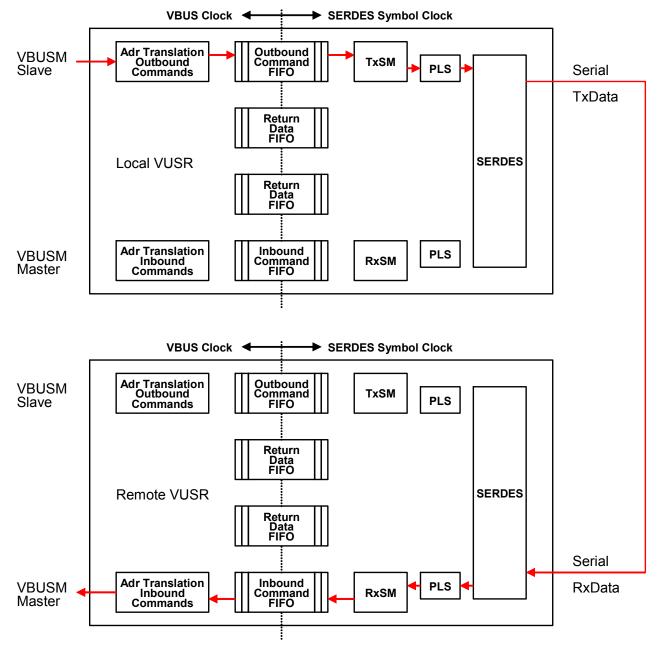

# 2.7.2 HyperLink Read Operations

This section discusses the HyperLink read operations. The read process is outlined in Procedure 2-2 and shown in Figure 2-7.

#### Procedure 2-2 HyperLink Read Operations

#### Step - Action

- 1 HyperLink receives a read request from its VBUSM slave port.

- 2 The read request is stored in the Outbound Command FIFO.

- **3** The read command is read from the Outbound Command FIFO and the egress address translation logic modify its address field and overlay the control information before it is encapsulated in a Read Request Packet.

- 4 The packet is encoded, serialized, and sent to the remote device.

- 5 The remote device receives the Read Request Packet through its HyperLink interface.

- 6 The received packet is deserialized, decoded, and written to the Inbound Command FIFO.

- 7 The read request packet is read from the Inbound Command FIFO and initiates a read request based on the address and control information which the ingress address translation logic generates from the received address field.

- 8 The read request is sent out through the HyperLink master VBUSM port to one of the slave end point in the remote device.

- **9** When the HyperLink in the remote device receives the read return data, the data is written to its Return Data FIFO before being serialized.

- 10 The read return data is sent out by the HyperLink interface in the remote device.

- **11** The read return data packet is received by the HyperLink interface, and it is Step 12:The read data is transferred on the local VBUSM slave interface.

- 12 The read data is transferred on the local VBUSM slave interface.

Steps 9 to 12 are repeated for all data phases within the read burst. HyperLink does not wait for the completion of the read data before it sends out the read return data packet. It forms the read data packet on every read return burst. The read request is larger than 256B, it is divided into multiple read requests, each of which has maximum 256B burst.

The data flow between two connected HyperLink modules is shown with arrows in Figure 2-7 on page 2-15, with the read access originating from the Local HyperLink device. The read data is returned by the remote HyperLink device and displayed with the dotted arrows.

## 2.7.3 HyperLink Format

HyperLink operates on 64-bit quanta. Each word in HyperLink is 64 bits and it is sent as a single element. For each transaction, HyperLink transmits to the remote device through control words and data words.

Each HyperLink packet includes one or two control words and multiple data words. The Control Word and Control Word Extension bit definitions are defined in section 0 and 0 respectively. The Control Extension field is only included in the packet if the packet type indicates extended control (ext=1). This provides a mechanism to augment

commands sent in the Control Word. The Control Extension is used to deal with configuration packet types, which is used to access the registers in the remote HyperLink module. The HyperLink module in KeyStone devices does not support control extension.

HyperLink supports the following packet formats and how it is constructed:

- Read request: c. only one control word

- Write request: cD or cdd..dD

- Interrupt packet:c

- Read data return: cdddD

- Write request with byte enable: cdd..dmD. An example of cddmD means packet wrote 32 bytes where the bytes 16-23 contained disabled byte enables

#### Where:

- I Idle

- I# Packet continuation where the # is the 'c' from the packet continued.

- c Control Word: Command, length, address, TransactionID, etc.

- e Extension Control Word:

- d data

- D the last data word

- m data with mask bytes

A data burst always starts with a control word. The control word defines the characteristics of the data burst. When the packet is throttled by the remote HyperLink receiver, the idle code is inserted into the data stream. When the flow control is lifted, the transaction can be continued with a control word. For example, a write burst is flow controlled: cdddIIIcddddD.

The example above shows what can happen to a Write Burst due to remote FIFO state changes. In HyperLink, the outbound transactions and the return data share the same physical link to the remote device. The outbound transactions and data return can be interleaved. However, the data return has higher priority than the outbound transactions.

This is an example of an outbound write transaction interrupted by a read return data burst. The 1 indicates the control word for the data return channel and 0 indicates the control word for the outbound write transaction:

#### IIIIcddddIcdddII11ddddII0dddddddddddddIIIII10ddDIIII11DIIII

From the idle stream, HyperLink receives a command, length, address, and start receiving data. A flow-enable was received for the command channel, but there is data to return so the Flowed is followed by a channel 1 descriptor (the command for return data actually indicates a channel 1), and the channel 1 packet is now under way. A flow is then received for channel 1, but it is soon disabled so the channel 1 packet continues. Again the flow is enabled for channel one, quickly after flow is released for channel 0 so the data continues for channel 0 when a flow is received again for channel 0. Channel 0 then receives a flow disable, completed its packet, and followed by channel 1 flow disable where the channel one packet is also completed.

Whenever a channel is resumed—either from idle or another channel—the control word is resent. Resending the control allows the receiver to identify where to associate the data burst.

#### 2.7.3.1 General Bus Control Word

The General Bus Control Word transfers bus commands that provide the capability to read and write remote HyperLink devices. Currently, there are four types of control words supported: write post, read, interrupt and read data return.

The control word for read and write share the same format.

#### Figure 2-8 Control Word for Read and Write

| Bit 63                  | Bit | Bit 56 to | Bit 53     | Bit 51 to | Bit | Bit 46 to | Bit | Bit 42 | Bit 34  | Bit      | Bit | Bit 4    |

|-------------------------|-----|-----------|------------|-----------|-----|-----------|-----|--------|---------|----------|-----|----------|

| to 58                   | 57  | 54        | to 52      | 48        | 47  | 44        | 43  | to 35  | to 7    | 6        | 5   | To 0     |

| Reserved<br>(all zeros) | dbg | cclsize   | Camod<br>e | extAdr    | 0   | CMD       | cfg | length | Address | Pri<br>v | Pri | Order ID |

#### Figure 2-9 Control Word for Read Return

| Bit 63                  | Bit | Bit 46 to     | Bit | Bit 42 | Bit 34 | Bit 29   | Bit 19 | Bit 16 | Bit 10 | Bit 7    |

|-------------------------|-----|---------------|-----|--------|--------|----------|--------|--------|--------|----------|

| to 48                   | 47  | 44            | 43  | to 35  | to 30  | to 20    | to 17  | To 11  | 8      | To 0     |

| Reserved<br>(all zeros) | 0   | CMD=<br>0b111 | cfg | Length | Align  | Reserved | Status | Priv   | Pri    | Order ID |

The control word for an interrupt packet is different from the read/write control word and contains some interrupt-specific information.

#### Table 2-7Control Word Encoding (Part 1 of 2)

| Field N   | Number of Bits | Description                                                                                                                                                                 |

|-----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBG       | 1              | EMUDBG - Indicate that a transaction comes from the debug subsystem. This comes from the VBUS transaction sideband information.                                             |

|           |                | 0b1:transaction comes from the debug subsystem                                                                                                                              |

|           |                | 0b0: non-debug transaction                                                                                                                                                  |

| CMD       | 3              | Command Type. Indicates the type of bus command being serviced.<br>000b = write                                                                                             |

|           |                | 100b = read                                                                                                                                                                 |

|           |                | 110b = write interrupt                                                                                                                                                      |

|           |                | 111b = return data/status                                                                                                                                                   |

|           |                | All other values are reserved.                                                                                                                                              |

| CCLSIZE   | 3              | Cache line wrap size. This field indicates the cache line size the cache line wrap operates on. This field comes from the received VBUS transaction.                        |

| CAMODE    | 2              | Address Mode. This field indicates the Address mode of the command. This comes from the received VBUS transaction.                                                          |

| EXTADR    | 4              | 4MSB bit of the address                                                                                                                                                     |

| ADDRESS28 | 28             | 28 LSB bits of the address indicates the virtual address the data is to be written or read.                                                                                 |

| CFG/EXT   | 1              | Configuration/Extension Flag. This flag indicates that a configuration access or the extension control word is present after the control word. It is set to 0               |

| LENGTH    | 8              | Length. Indicates the length in bytes of the transaction.                                                                                                                   |

| PRIV      | 1              | Indicates the privilege that the command has been sent with. This comes from the VBUS transaction side band signals directly.<br>1 = supervisor mode<br>0 = supervisor mode |

|           |                | ,                                                                                                                                                                           |

-

. . . . . .

. \_

...

----

- - - - -

| Table 2-7 | Control Wo     | rd Encoding (Part 2 of 2)                                                                                                                                                                                                                                                                                                   |

|-----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field     | Number of Bits | Description                                                                                                                                                                                                                                                                                                                 |

| PRI       | 1              | PRI indicates the priority of the request. HyperLink only supports the two priorities for outbound transactions. If the received command's priority is between 0 and 3, the PRI is set to 0. If the received command's priority is between 4 to 7, the PRI is set to 1.<br>0 = priority 0<br>1 = priority 4                 |

| ORDERID   | 5              | Order ID. Indicates the transaction identifier associated with the request. All request with the same ORDERID will be services in the same order as the command arrival. Commands with differing ORDERID fields can be processed in any order. The ORDERID field is assigned by hardware and it is transparent to the user. |

| STATUS    | 3              | Status. This field is the status for read and write responses.                                                                                                                                                                                                                                                              |

#### Figure 2-10 Control Word for Interrupt Packet

| Bit 63                  | Bit | Bit 46 to     | Bit | Bit 35        | Bit 31 to | Bit 16 | Bit 10 | Bit 7    |

|-------------------------|-----|---------------|-----|---------------|-----------|--------|--------|----------|

| to 48                   | 47  | 44            | 43  | to 32         | 24        | To 11  | 8      | To 0     |

| Reserved<br>(all zeros) | 0   | CMD=<br>0b110 | cfg | MPU<br>select | vector    | Priv   | Pri    | Order ID |

Although multiple bits are assigned for the PRIV and PRI fields, only the LSB bit is used.

The MPU select field carries the information for microprocessor select bit. And the vector field is assigned 8 bits, but only the last 5 LSB bits are used in KeyStone devices. The unused bits are set to zeros.

Even though eight bits are assigned for order ID, only the five LSB are used. The three MSB bits are zeros.

# 2.7.4 Address Translation

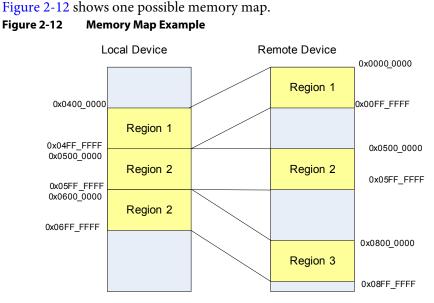

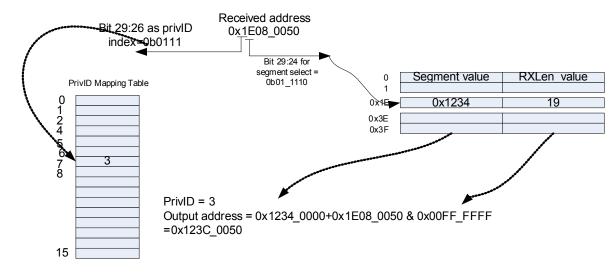

HyperLink has independent ingress address translation blocks and egress address translation blocks. The main function of the ingress address translation is to overlay the control information into the address field. The main function of the egress address translation is to remap the incoming address to different memory regions. HyperLink supports up to 64 different memory regions. The starting address of each memory region can be placed on any 64 KB address boundary, and the size of each memory mapped region can be sized to a power of two, starting at 256 B. In KeyStone devices, the maximum memory region size is 256MB. The address translation is done on a per-packet basis.

Some of the transaction characteristics have been embedded into the control word, such as priority, supervisor, and use mode, etc. The PRIVID and security characters are embedded in the address field.

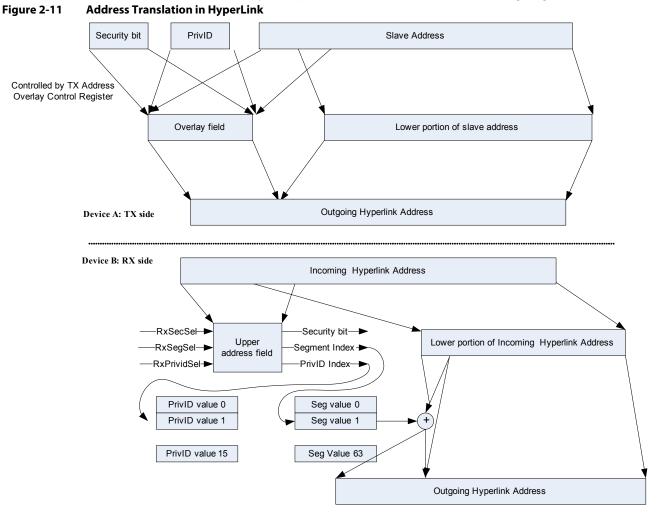

Figure 2-11 shows how the address translation done at both the TX and RX side. On the TX side, the TX overlay control register determines how the security bit and PRIVID overlay on top of the slave address to form the outgoing address.