Altera FPGA Cores

Overview

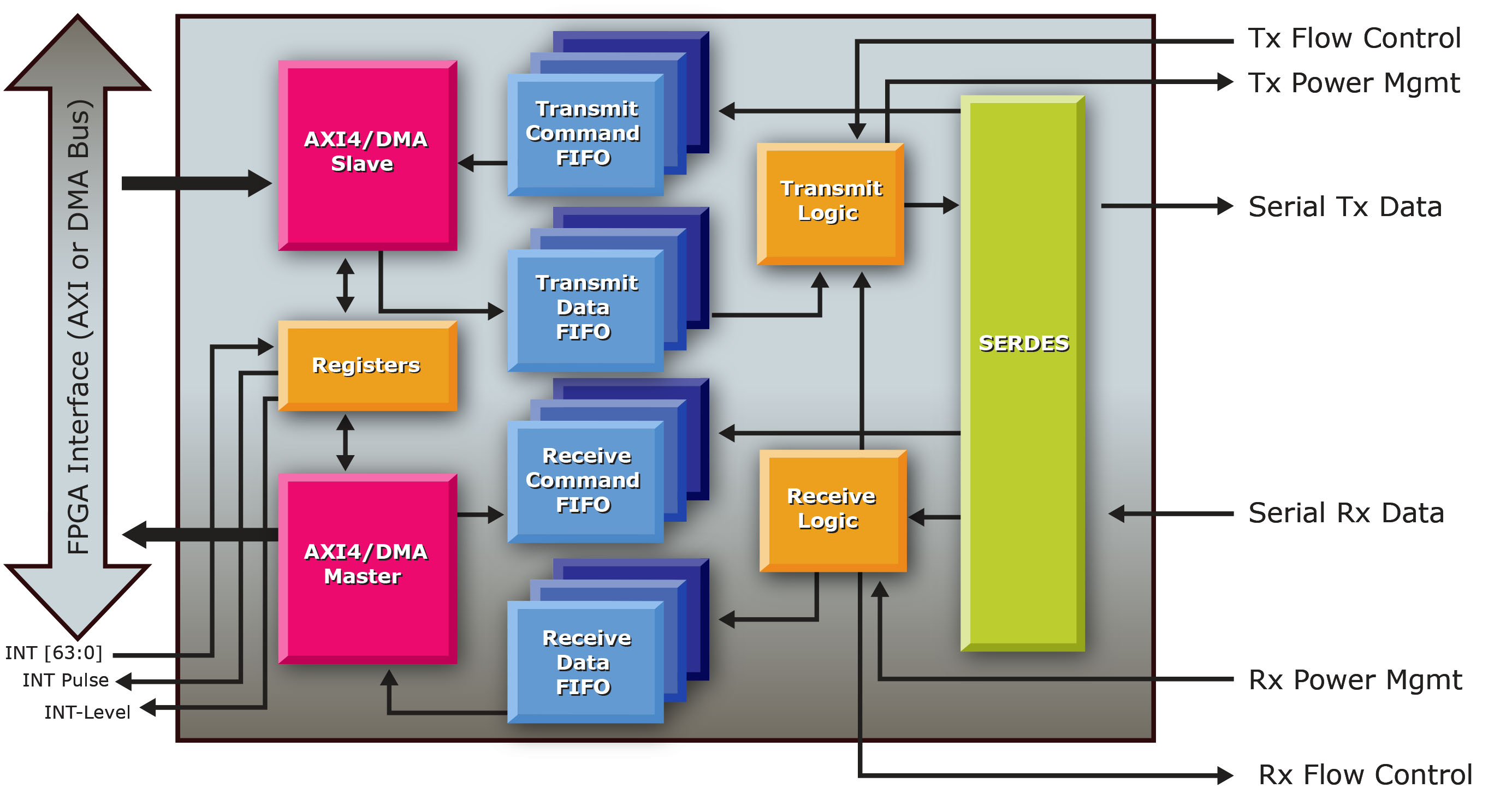

The Integretek HyperLink FPGA core leverages the proven TI HyperLink technology connecting your FPGA design to a Texas Instruments C66X multi-core DSP at link rates up to 25 Gb/s. Developers can choose either an industry standard AXI4 bus or DMA interface. The HyperLink IP is available in both a x4 lane configuration and low cost x1 lane configuration.

Features

- Up to 25Gbps lane rate (4 lane) *

- Point-to-point connection

- Link self-initializes

- Supports multiple outstanding read, write and interrupt transactions

- Simple packet-based transfer protocolfor memory mapped access

- AXI4 Interface Complies with AMBA AXI Protocol V2.0

- 64 user defined interrupt inputs, level and pulse sensitive

- AXI4 Slave (transmit to DSP and Control Register access)

- AXI4 Master (receive from DSP)

- Optional DMA Interface

Verification

A Verilog environment is provided that can be adapted to your application. The environment includes:

- Testbench

- Sample Tests

- Scripts

Deliverables

The core package includes the following:

- Encrypted RTL

- Testbench and verification environment

- User Guide Documentation

- Compilation, simulation, and programming ready example project

- Technical Support

FPGA Interface

The HyperLink IP Core provides either an AXI4 master and slave bus interface for initiating single and burst HyperLink transactions or a vectored DMA interface.

AXI4 Interface

- AXI4 Interface Complies with AMBA AXI Protocol V2.0

- 64 user defined interrupt inputs, level and pulse sensitive AXI4 Slave (transmit to DSP and Control Register access)

- 8,16,32,64,128 and 256 bit single cycle AXI accesses

- 32,64,128 and 256 bit multi‐beat AXI burst accesses

- AXI INCR and WRAP Burst Types

- Up to 16 outstanding write requests

- Up to 16 outstanding read requests with unique read id’s

- AXI Private and Secure Access Types

AXI4 Master (receive from DSP)

- AXI INCR and WRAP Burst Types

- Up to 16 outstanding read requests with unique read id’s

- AXI Private and Secure Access Types

DMA Interface

The HyperLink Vectored DMA interface provides a simple control interface and memory bus connections for initiating single and burst HyperLink transactions. All HyperLink memory transactions are performed without any user setup or intervention.

- DMA burst size 16Kbyte per chain, total of 16 chains (Write and Read have 16 dedicated chains each)

- Maximum chained DMA burst size of 256Kbyte

- DMA Slave (write to DSP, read from DSP) interface is byte addressable for both source and destination addresses

- 32 byte (256bit) Write and Read data interfaces for Slave (write to DSP, read from DSP) interface

- DMA Master (write from DSP, read to DSP) interface is byte addressable for both source and destination addresses

- 32 byte (256bit) Write and Read data interfaces for Master (write from DSP, read to DSP) interface

- Single transaction write, read interfaces on DMA Slave side (used for HyperLink configuration)

- Independent write, read DMA control and configuration interfaces

Supported Devices

| FAMILY | DEVICE | SPEED GRADES | LANE/QUAD SPEEDS (GBPS) | TESTED DEV KIT | CORE STATUS | CONNECTIVITY CARD |

|---|---|---|---|---|---|---|

| Arria 10 | Arria V 10 GX | All | 1.25/5,3.125/12.5,6.25/25 | DK-DEV-10AX115S-A | Released | FMC-951 |

| Arria V | Arria V GX | All | 1.25/5,3.125/12.5 | DKST-5AGXB3N | Released | HSMC-950 |

| Arria V | Arria V GT | All | 1.25/5,3.125/12.5 | Released | HSMS-950 | |

| Arria V | Arria V GZ | All | 1.25/5,3.125/12.5 | 5AGZDEMO000011 | Released | HSMC-951 |

| Cyclone V | Cyclone V GX | All | 1.25/5,3.125/12.5 | DKDV-5CGXC7 | Released | HSMC-950 |

| Stratix V | Stratix V GX | All | 1.25/5,3.125/12.5,6.25/25 | DK-DEV55GXEA7N | Released | HSMC-951 |

| Stratix IV | EOL |