# **HyperLink High Speed DSP Interface Core**

Open up your FPGA design to the power of the Texas Instruments DSP with the *Integretek HyperLink High Speed DSP Interface Core*. The core provides a high speed, low pin count bi-directional interface connecting your FPGA design to a Texas Instruments C66X multi-core DSP.

25 Gbps Link Rate (4 lane)

Low Pin Count Interface

AXI or DMA Interface

x1 or x4 Configurations

Based on TI Proprietary Technology

## **FEATURES**

- Up to 25Gbps transfer rate (4 lane) \*

- SERDES data signals

- Dedicated LVCMOS pins for flow control and power management

- Point-to-point connection

- Link self-initializes

- Supports multiple outstanding read, write and interrupt transactions

- Simple packet-based transfer protocol for memory mapped access

- Available with AXI or DMA Interface

- Internal SERDES diagnostic loopback mode

- 64 user defined interrupt inputs, level and pulse sensitive

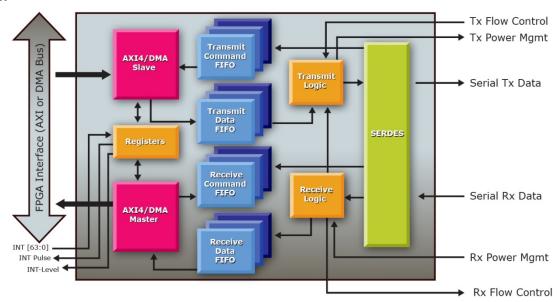

Interface options include an AXI4 master/slave bus interface or vectored DMA interface.

- AXI4 Slave (transmit to DSP and Control Register access)

- 8,16,32,64,128 and 256 bit single cycle AXI accesses

- 32,64,128 and 256 bit multi-beat AXI burst accesses

- Up to 16 outstanding write/read requests

- AXI4 Master (receive from DSP)

- Up to 16 outstanding read requests with unique read id's

- AXI Private and Secure Access Types

- DMA burst size 16Kbyte per chain, total of 16 chains (Write and Read have 16 dedicated chains each)

- Maximum chained DMA burst size of 256Kbyte

- Independent write, read DMA control and configuration interfaces

## **BLOCK DIAGRAM**

### **DELIVERABLES**

The core package includes the following:

- Encrypted RTL

- Testbench and verification environment

- User Guide Documentation

- •Compilation, simulation, and programming ready example project

- Technical Support

### **VERIFICATION**

A Verilog environment is provided that includes:

- Testbench

- •Sample Tests

Tests represent typical use cases

- Adaptable to your application

- Scripts

## WARRANTY and SUPPORT

The core as delivered is warranted against defect for one hundred days from purchase delivery date. Phone and Email product support is included for a period of thirty days. Optional product maintenance and support agreements are available.

### SUPPORTED DEVICES

The HyperLink Interface core is available for the following devices:

ALTERA XILINX

Stratix V GX Kintex-7 GTX

Arria V GX Virtex-7 GTX

Arria V GT Virtex-7 GTH

Arria V GZ Artix-7 GTP

Cyclone V GX Kintex UltraScale GTH

Arria 10 GX

Additional device families are being added, please check the Integre website for the latest device list.

## **COMPANION PRODUCTS**

Integre offers the following products to assist with your HyperLink development:

FMC-950/951 HyperLink Connectivity Card With LVDS for FMC Platforms

HSMC-950/951 HyperLink Connectivity Card With LVDS for HSMC Platforms

950-PLUG-LB HyperLink Loopback Plug

IP-HyperLink-Analyzer HyperLink Analyzer Kit for Monitoring Data in Real Time

IP-HyperLink-Maint Twelve month IP Maintenance extension.

#### **NOTES**

\*Supported rates vary depending on FPGA family and device. Future products slated for 50Gbps performance.

All trademarks are property of their respective owners.